How to Diagnose and Fix Complex Bus Contention Issues in Multi-Core Processors: Techniques for Advanced System Stability

Introduction to Bus Contention Issues in Multi-Core Processors

In today’s tech-driven world, multi-core processors have become the backbone of performance in our laptops and desktop systems. However, with great power comes great responsibility—and complexity. One of the most challenging issues that can arise in these advanced architectures is bus contention. This phenomenon occurs when multiple cores try to access shared resources simultaneously, leading to slowdowns and system instability.

For those diving deep into the realm of computing, diagnosing and fixing bus contention issues may seem daunting. But fear not! By understanding what causes these conflicts and applying specific techniques, you can enhance your laptop’s reliability and overall performance. Whether you’re a seasoned technician or an enthusiastic DIY-er looking to improve your device’s efficiency, unraveling the mysteries of bus contention will empower you to tackle complex challenges head-on. Let’s delve into this critical topic together!

Understanding the Root Causes of Bus Contention

Bus contention in multi-core processors arises from various factors. At its core, it involves multiple cores trying to access the same memory resource simultaneously.

One primary cause is insufficient bandwidth. If the bus cannot handle data requests from all active cores, delays occur. This bottleneck leads to a slowdown in processing speed and can disrupt overall system performance.

Another factor is poor scheduling of tasks among the cores. When workloads aren’t evenly distributed, certain cores become overloaded while others remain underutilized. This imbalance exacerbates contention issues.

Moreover, latency plays a significant role. High-latency operations hinder rapid communication between cores and memory, further complicating contention scenarios.

Outdated hardware might lack modern features designed to mitigate these challenges effectively. Understanding these root causes helps identify appropriate strategies for resolution.

Techniques for Diagnosing Bus Contention Issues

Diagnosing bus contention issues in multi-core processors requires a systematic approach. Start by monitoring system performance metrics. Tools like CPU profilers can reveal bottlenecks and help identify spikes in resource usage.

Next, conduct stress tests to simulate heavy workloads. This lets you observe how the processor behaves under pressure, revealing underlying contention problems that might not appear during normal operation.

Utilize logging tools to track memory access patterns. Analyzing these logs can highlight conflicts between cores trying to access shared resources simultaneously.

Another effective technique involves examining thread behavior. Using debuggers, you can trace thread execution and pinpoint where delays occur due to contention.

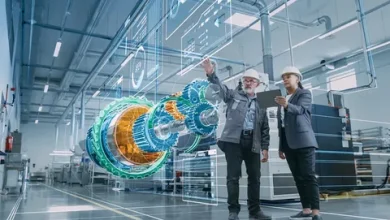

Consider visualizing data flow within your system architecture. Graphical representations of bus activity can make it easier to spot contention hotspots that require attention or adjustment.

Fixing Bus Contention through Processor Affinity Management

Processor affinity management is a strategic approach to mitigate bus contention in multi-core processors. By assigning specific tasks to designated cores, it minimizes the chances of overloading a single bus.

This method enhances resource allocation and ensures that workloads are evenly distributed across available cores. It prevents scenarios where multiple processes compete for the same memory resources, which can lead to significant delays.

Utilizing operating system tools or custom scripts allows developers to set affinities dynamically based on workload demands. This adaptability enables systems to respond effectively under varying load conditions.

Additionally, monitoring toolkits help identify bottlenecks in real-time. With this data, adjustments can be made proactively, ensuring that high-demand applications operate smoothly without unnecessary interference from other processes.

Implementing Efficient Cache Coherence Protocols

Efficient cache coherence protocols play a crucial role in managing data consistency across multiple cores. They ensure that when one core updates a value in its cache, other cores can see the most recent version of that data.

One popular protocol is MESI (Modified, Exclusive, Shared, Invalid), which allows for streamlined communication between caches. By minimizing unnecessary traffic and ensuring timely updates, it enhances overall system performance.

Another method involves using directory-based coherence mechanisms. This approach reduces bus traffic by tracking the location of cached copies and only notifying relevant processors about changes.

Implementing these protocols requires careful consideration of workload patterns and processor architecture. Tailoring the implementation to specific use cases leads to significant improvements in stability and efficiency.

Adopting efficient cache coherence methods can lead to smoother operation within multi-core systems while mitigating potential bottlenecks caused by bus contention.

Utilizing High-Speed Interconnects to Reduce Bus Congestion

High-speed interconnects are revolutionizing how data flows between cores in multi-core processors. By providing a robust communication pathway, these interconnects significantly reduce bus congestion.

Implementing technologies such as InfiniBand or PCI Express can enhance throughput. This ensures that data packets move swiftly across the system without bottlenecks.

Moreover, advanced routing techniques optimize traffic patterns. Instead of clogging a single bus, multiple pathways allow for efficient use of resources.

Integrating high-speed links also facilitates better cache coherence management. As caches synchronize more quickly, the latency issues often seen with slower connections diminish.

With increasing demand for performance in applications ranging from gaming to scientific simulations, investing in high-speed interconnect solutions is vital for maintaining system integrity and responsiveness.

Conclusion: The Importance of Addressing Complex Bus Contention Issues for System Stability and Performance

Addressing complex bus contention issues is crucial for enhancing system stability and performance. Multi-core processors are designed to handle multiple tasks efficiently, but when these processors face bus contention, it can lead to significant slowdowns and inefficiencies.

Understanding the root causes of these issues helps in implementing effective solutions. Techniques like processor affinity management ensure that tasks are assigned optimally across cores, minimizing competition for resources. Efficient cache coherence protocols play a key role in maintaining data consistency while reducing latency.

Furthermore, utilizing high-speed interconnects can significantly alleviate congestion on the shared buses, allowing for smoother communication between cores. By prioritizing these strategies, users can not only resolve existing problems but also prevent future occurrences.

An experienced laptop repair expert in Perth mentioned that grasping the intricacies of bus contention is essential for optimizing laptop performance and ensuring reliable operation. For those involved in laptop repair or system optimization, understanding these technical challenges can empower technicians to provide better service, ensuring systems run smoothly under heavy workloads and maintain their performance over time. The focus on addressing such technical challenges ultimately leads to more resilient computing environments that cater effectively to user demands.